BIASING VOLTAGE DEVIDER

A. TUJUAN

[KEMBALI]

Pembagi Tegangan di Rangkaian Elektronika adalah untuk membagi Tegangan Input menjadi satu atau beberapa Tegangan Output yang diperlukan oleh Komponen lainnya didalam Rangkaian.

B. KOMPONEN

[KEMBALI]

1. Resistor

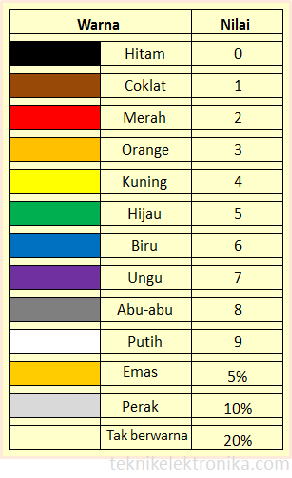

Resistor atau hambatan adalah salah satu komponen elektronika yang memiliki nilai hambatan tertentu, dimana hambatan ini akan menghambat arus listrik yang mengalir melaluinya. Umumnya terdapat 4 Gelang di tubuh Resistor, tetapi ada juga yang 5 Gelang.

Gelang warna Emas dan Perak biasanya terletak agak jauh dari gelang warna lainnya sebagai tanda gelang terakhir. Gelang Terakhirnya ini juga merupakan nilai toleransi pada nilai Resistor y

2. Capasitor

Kode : 473Z

Nilai Kapasitor = 47 x 103

Nilai Kapasitor = 47 x 1000

Nilai Kapasitor = 47.000pF atau 47nF atau 0,047µF

Huruf dibelakang angka menandakan Toleransi dari Nilai Kapasitor tersebut, Berikut adalah daftar Nilai Toleransinya :

B = 0.10pF

C = 0.25pF

D = 0.5pF

E = 0.5%

F = 1%

G= 2%

H = 3%

J = 5%

K = 10%

M = 20%

Z = + 80% dan -20%

3. Transistor

4. Ground

C. BIASING VOLTAGE-DIVIDER

Pengaturan bias pembagi tegangan yang diterapkan pada

amplifier transistor BJT juga diterapkan pada amplifier FET seperti yang

ditunjukkan oleh Gambar. 6.20

Konstruksi dasarnya persis sama, tetapi analisis dc

masing-masing sangat berbeda. IG =0

A untuk amplifier FET, tetapi besarnya IB untuk

amplifier BJT common-emitor dapat mempengaruhi level arus dan tegangan dc di

sirkuit input dan output. IB menyediakan hubungan antara

sirkuit input dan output untuk konfigurasi pembagi tegangan BJT sementara VGS akan

melakukan hal yang sama untuk konfigurasi FETJaringan Gambar 6.20 digambar ulang seperti yang ditunjukkan pada Gambar. 6.21

untuk analisis dc

Semua kapasitor, termasuk kapasitor pintas CS, telah diganti dengan yang setara "sirkuit terbuka".

Hukum Kirchhoff saat ini mengharuskan iR1 =IR2 dan

setara rangkaian seri muncul ke kiri dari angka dapat digunakan untuk menemukan

tingkat VG.Tegangan VG,sama

dengan tegangan R2,dapat ditemukan dengan menggunakan aturan voltagedivider

sebagai berikut :

Menerapkan hukum tegangan Kirchhoff ke arah jarum jam untuk loop

ditunjukkan pada Gambar 6.21 akan menghasilkan :

Jika kita memilih ID sebagai

0 mA, pada dasarnya kita menyatakan bahwa kita berada di suatu tempat pada

sumbu horizontal. Lokasi yang tepat dapat ditentukan hanya dengan mengganti ID _ 0

mA ke Persamaan. (6.16) dan menemukan nilai yang dihasilkan dari VGS sebagai

berikut:

Hasilnya menentukan bahwa setiap kali kita plot Persamaan. (6.16),

jika kita memilih sayaD _ 0 mA, nilai VGS untuk

plot akan VG volt. Titik yang baru saja ditentukan muncul pada Gambar

6.22.

Untuk titik lain,gunakan fakta bahwa pada

titik mana pun pada sumbu vertikal VGS =0 V dan

selesaikan untuk nilai yang dihasilkan dari ID:

Pada Gambar 6.22. Dua poin yang didefinisikan di atas

memungkinkan gambar garis lurus untuk mewakili Persamaan. (6.16). Perpotongan

garis lurus dengan kurva transfer di wilayah sebelah kiri sumbu vertikal akan

menentukan titik operasi dan level yang sesuai dari ID dan

VGS. Karena persimpangan pada

sumbu vertikal ditentukan oleh ID _ VG/RS dan

VG ditetapkan oleh jaringan

input, peningkatan nilai RS akan

mengurangi tingkat ID persimpanganseperti

yang ditunjukkan pada Gambar 6.23. Hal ini cukup jelas dari Gambar 6.23 bahwa: Peningkatan

nilai RS menghasilkan nilai diam yang lebih rendah dari ID dan lebih banyak nilai negatif dari VGS.

Setelah nilai-nilai diam IDQ dan VGSQ ditentukan, analisis jaringan yang tersisa dapat dilakukan dengan cara biasa. Yaitu,

D. PRINSIP KERJA

[KEMBALI]

Setiap beban yang kita pasang pada setiap terminal output suatu rangkaian akan membuat tegangan output tersebut turun akibat hubungan parallel antara tahanan pada terminal output dengan tahanan beban. Setiap resistansi atau tahanan yang terhubung parallel akan membuat tahanan totalnya lebih kecil dari kedua tahanan yang terhubung parallel tersebut, akibatnya dengan turunya tahanan pada terminal tersebut maka pada pembagian tegangan dengan rangkaian seri yang lain terminal tadi akan memperoleh tegangan yang lebih kecil.

E. GAMBAR RANGKAIAN

[KEMBALI]

(gambar 1)

(gambar 1)

(gambar 2)

(gambar 2)

F. VIDEO TUTORIAL

[KEMBALI]

lihat di sini ( video gambar 1)

(gambar 2)

G. CONTOH SOAL

[KEMBALI]

1.Tentukan berikut ini untuk jaringan Gambar. 6.24. (a) IDQ dan VGSQ, .(b) VD., (c) VS, (d) VDS, dan (e) VDG

Persamaan jaringan ditentukan oleh Garis bias yang dihasilkan muncul pada Gambar 6.25 dengan nilai diam

(e) Meskipun jarang diminta, tegangan VDG dapat dengan mudah ditentukan dengan menggunakan

2. Tentukan berikut ini untuk jaringan Gambar 6.26. (a) IDQ dan VGSQ.(b) VDS.(c) VD. dan (d) VS

[KEMBALI]

Setiap beban yang kita pasang pada setiap terminal output suatu rangkaian akan membuat tegangan output tersebut turun akibat hubungan parallel antara tahanan pada terminal output dengan tahanan beban. Setiap resistansi atau tahanan yang terhubung parallel akan membuat tahanan totalnya lebih kecil dari kedua tahanan yang terhubung parallel tersebut, akibatnya dengan turunya tahanan pada terminal tersebut maka pada pembagian tegangan dengan rangkaian seri yang lain terminal tadi akan memperoleh tegangan yang lebih kecil.

E. GAMBAR RANGKAIAN

[KEMBALI]

(gambar 1)

(gambar 1) (gambar 2)

(gambar 2) F. VIDEO TUTORIAL

[KEMBALI]

lihat di sini ( video gambar 1)

(gambar 2)

G. CONTOH SOAL

[KEMBALI]

1.Tentukan berikut ini untuk jaringan Gambar. 6.24. (a) IDQ dan VGSQ, .(b) VD., (c) VS, (d) VDS, dan (e) VDG

Solusi

(a)

Untuk karakteristik transfer, jika ID=IDSS/ 4 =

8 mA / 4 _ = 2 mA, maka VGS=VP/ 2 = 4 V / 2 = 2 V. The kurva yang dihasilkan

yang mewakili persamaan Shockley muncul pada Gambar 6.25.Persamaan jaringan ditentukan oleh Garis bias yang dihasilkan muncul pada Gambar 6.25 dengan nilai diam

(e) Meskipun jarang diminta, tegangan VDG dapat dengan mudah ditentukan dengan menggunakan

2. Tentukan berikut ini untuk jaringan Gambar 6.26. (a) IDQ dan VGSQ.(b) VDS.(c) VD. dan (d) VS

Solution

(a) persamaan untuk VGS dalam hal ID diperoleh dengan menerapkan hukum tegangan Kirchhoff ke bagian input dari jaringan sebagai digambar ulang pada Gambar. 6.27.

Hasilnya adalah persamaan yang dapat ditumpangkan pada karakteristik transfer

menggunakan prosedur yaitu

Poin plot yang dihasilkan diidentifikasi pada Gambar 6.28.

Karakteristik transfer digambarkan menggunakan titik plot yang dibuat oleh VGS=VP/ 2 = -3 V / 2 = -1,5 V dan ID= IDSS/ 4 = 9 mA / 4 = 2,25 mA, seperti juga muncul pada Gambar 6.28. Titik operasi yang dihasilkan menetapkan level diam berikut ini:

(b) Menerapkan hukum tegangan Kirchhoff ke sisi output pada Gambar 6.26 akan menghasilkan Pengganti IS= ID dan

penataan ulang memberikan yang untuk contoh ini menghasilkan

H. LINK DOWNLOAD 1. Materi klik di sini

2. Gambar rangkaian

a. gambar 1 klik di sini

b. gambar 2 klik di sini

3. Video tutorial

a. gambar 1 klik di sini

b. gambar 2 klik di sini

4. Simulasi rangkaian proteus

a. rangkaian 1 klik di sini

b. rangkaian 2 klik di sini

5. Datasheet klik di sini

Tidak ada komentar:

Posting Komentar