A. TUJUAN [KEMBALI]

1. mengetahui macam-macam rangkaian flip-flop

2. megetahui mavam-macam timing flip-flop

B. ALAT DAN BAHAN [KEMBALI]

a. 74111

IC Monolitik, Yaitu IC yang berdiri sendiri artinya dalam satu IC monolitik ini hanya menjalankan/mengatur satu blok rangkaian saja dan tidak tergabung dengan IC yang lain. Umumnya IC monolitik ini biasanya kebanyakan didapati pada radio dan televise.

b. clock

pembuat

jam menentukan waktu transisi maksimum (waktu naik dan turun) untuk

keluaran menanggapi dengan benar. Jika angka-angka yang ditentukan ini

terlampaui, flip-flop mungkin merespons secara tidak menentu atau bahkan

mungkin tidak menanggapi sama sekali. Parameter ini khusus keluarga

logika dan tidak ditentukan untuk individu perangkat. Waktu transisi

maksimum yang diizinkan untuk perangkat TTL jauh lebih kecil daripada

untuk CMOS perangkat. Juga, dalam keluarga TTL yang luas, itu bervariasi

dari satu subfamili ke subfamili lainnya

c. nand

tabel kebenaran

Perhatikan pada tabel kebenaran untuk gerbang NAND dibuat dengan membalikkan keluaran Gerbang AND. Gerbang NAND biasanya digunakan pada indistri dan digunakan secara luas dalam semua peralatan digital. Yang harus kalian pahami atau ketahui adalah gerbang NAND memilki keluaran RENDAH (logik 0) bila semua masukan TINGGI (logik 1). Kolom keluaran pada baris 4 dalam tabel kebenaran NAND menghasilkan suatu keluaran 0 sedangkan semua baris lain menghasilkan keluaran 1.

C. DASAR TEORI [KEMBALI]

10.9.1 Set-Up and Hold Times

10.9.2 Propagation Delay

10.9.3 Clock Pulse HIGH and LOW Times

10.9.4 Asynchronous Input Active Pulse Width

10.9.5 Clock Transition Times

pembuat jam menentukan waktu transisi maksimum (waktu naik dan turun) untuk keluaran menanggapi dengan benar. Jika angka-angka yang ditentukan ini terlampaui, flip-flop mungkin merespons secara tidak menentu atau bahkan mungkin tidak menanggapi sama sekali. Parameter ini khusus keluarga logika dan tidak ditentukan untuk individu perangkat.

10.9.6 Maximum Clock Frequency

Ini adalah frekuensi tertinggi yang dapat diterapkan ke input jam. Jika angka ini terlampaui, di sana tidak ada jaminan bahwa perangkat akan bekerja dengan andal dan benar. Angka ini mungkin sedikit berbeda dari perangkat ke perangkat dengan nomor jenis yang sama.

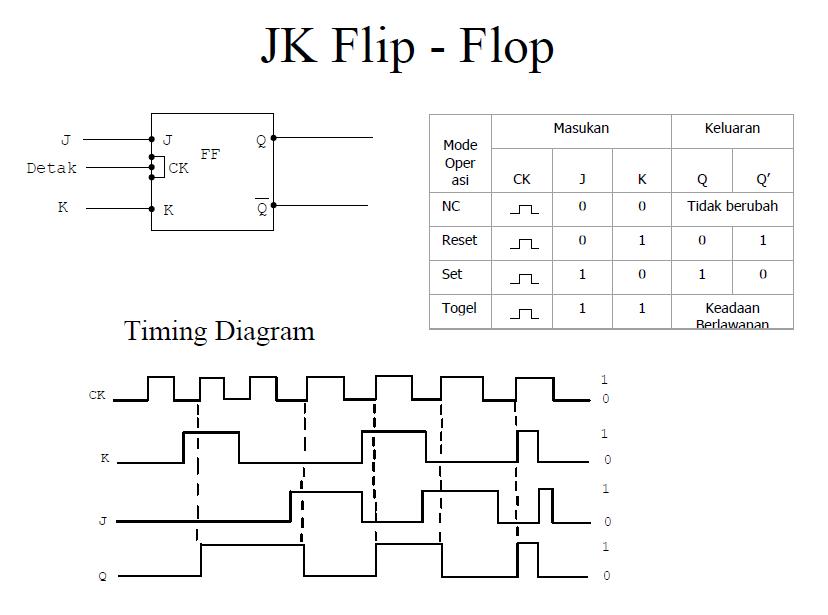

D. GAMBAR RANGKAIAN [KEMBALI]

Prinsip Kerja :

E. VIDEO [KEMBALI]

F. LINK DOWNLOAD [KEMBALI]

1. materi klik di sini

2. html klik di sini

3. rangkaian proteus klik di sini

4. video klik di sini

5. datasheet

a. 74111 klik di sini

b. nand klik di sini

G. CONTOH SOAL [KEMBALI]

1.Apa yang akan terjadi Jika Clock

Transition Times melebihi angka yang telah ditentukan ?

a. keluaran menanggapi dengan benar.

b. merespons secara tidak menentu atau bahkan mungkin tidak menanggapi sama

sekali.

c. akan berkerja dengan benar dan tidak memiliki gangguan apapun

2. Apa itu Asynchronous Input Active

Pulse Width ?

Jawab : durasi waktu minimum di mana masukan asinkron (PRESET atau CLEAR) harus

dijaga dalam keadaan aktif, biasanya RENDAH, agar keluaran merespons dengan

benar.

H. PROBLEM [KEMBALI]

1.

Apa yang akan terjadi ketika set up times tidak stabil ketika transisi jam

aktif ?

jawab : yang terjadi adalah keluaran flip-flop tidak akan merespons

dengan andal pada transisi jam. bahkan bisa hadi perangkat tidak akan

bekerja

2.Bagaimana

set-up times flip-flop 74ALS109A agar berkeja dengan baik ?

jawab : Waktu set-up dalam kasus 74ALS109A, yang merupakan flip-flop yang

dipicu tepi positif J-K ganda milik keluarga logika Schottky TTL daya rendah ,

adalah 15 ns. Juga, file asynchronous input, seperti PRESET dan CLEAR, jika

ada, harus tidak aktif sebelum transisi jam untuk periode waktu minimum

tertentu jika output harus merespons sesuai input sinkron. Dalam kasus ini dari

74ALS109A, waktu pengaturan input asynchronous adalah 10 ns. Waktu penyetelan

masukan asinkron untuk input PRESET dan CLEAR rendah aktif , dengan asumsi

edge-triggered positif flip-flop

I. SOAL PILIHAN GANDA [KEMBALI]

1. Maximum Clock Frequency adalah

a. frekuensi tertinggi yang dapat diterapkan ke output jam

b. frekuensi terendah yang dapat diterapkan ke input jam

c. frekuensi tertinggi yang dapat diterapkan ke input jam

jawaban : C

2. Set-Up (Pengaturan Waktu) adalah

a. periode waktu minimum untuk input sinkron (misalnya, R, S, J, K dan D

dan input asinkron (misalnya, PRESET dan CLEAR)

b. periode waktu maksimum untuk input sinkron (misalnya, R, S, J, K dan D dan

input asinkron (misalnya, PRESET dan CLEAR)

c. frekuensi minimum untuk input sinkron (misalnya, R, S, J, K dan D dan input

asinkron (misalnya, PRESET dan CLEAR)

Jawaban : A

Tidak ada komentar:

Posting Komentar